## Ferroelectric-gate Field Effect Transistors Based Nonvolatile Memory Devices Using p-type Si Nanowire Conducting Channel

**Dae Joon Kang**, Ngoc Huynh Van, Jae Hyun Lee<sup>1</sup>, Jung Inn Sohn<sup>2</sup>, Seung Nam Cha<sup>2</sup>, Dong Mok Hwang<sup>1</sup>, Jongmin Kim<sup>2</sup>

BK21 Physics Research Division, Department of Energy Science, Institute of Basic Science, SKKU Advanced Institute of Nanotechnology, Sungkyunkwan University, Suwon 440-746, Republic of Korea.

School of Advanced Materials Science and Engineering, SKKU Advanced Institute of Nanotechnology, Sungkyunkwan University, Suwon 440-746, Republic of Korea.

<sup>2</sup>Frontier Research Lab., Samsung Advanced Institute of Technology, Republic of Korea. djkang@skku.edu

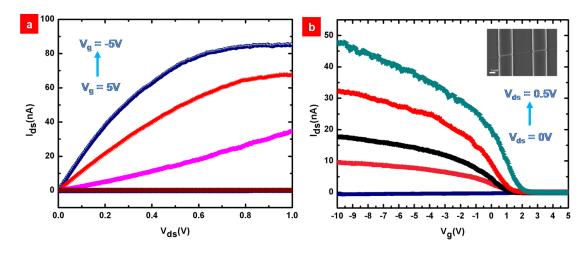

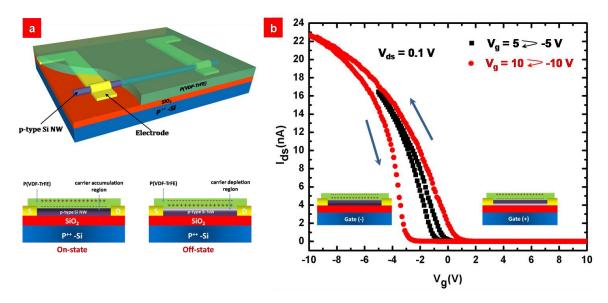

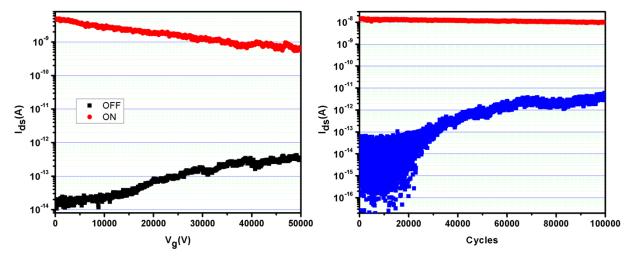

Ferroelectric-gate field effect transistor (FEFET) based memory using a nanowire as a conducting channel has many desirable features including small cell size, low-voltage operation, low power consumption, fast programming/erase speed and non-volatility [1]. We successfully fabricated a ferroelectric nonvolatile memory device using a p-type Si nanowire coated with organic ferroelectric PVDF via a low temperature fabrication processing technique [2,3]. The device performance was carefully characterized in terms of their electrical transport, retention and endurance time. <sup>[3]</sup>. Our FEFET memory devices exhibit excellent memory characteristics with a large modulation in channel conductance between ON and OFF states exceeding 10<sup>5</sup>; long retention time of over 5x10<sup>4</sup> s and high endurance of over 10<sup>5</sup> cycles while maintaining ON/OFF ratio over 10<sup>3</sup> (See Fig. 1, 2 and 3). This result offers a viable way to fabricate a high performance high-density nonvolatile memory device using a low temperature fabrication processing technique, which makes it suitable for future flexible electronics.

## References

- [1] Ma, T. P. & Han, J.-P. "Why is Nonvolatile Ferroelectric Memory Field-Effect Transistor Still Elusive?" *IEEE Electron Device Letters*, 2002, 23, 386-388

- [2] Minghua Tang, Xiaolei Xu, Zhi Ye, Yoshihiro Sugiyama, and Hiroshi Ishiwara "Impact of HfTaO buffer layer on data retention characteristics of ferroelectric-gate FET for nonvolatile memory applications" IEEE Transactions on Electron Devices, 58:370-375, 2011.

- [3] Hiroshi Ishiwara "Current status of ferroelectric-gate Si transistors and challenge to ferroelectric-gate CNT transistors" Current Applied Physics, 9:S2-S6, 2009.

## **Figures**

Fig.1. Electric transport properties of single Si NW FET device under ambient condition. (a)  $I_{\rm ds}$ - $V_{\rm ds}$  output characteristics and (b)  $I_{\rm ds}$ - $V_{\rm g}$  transfer characteristics at  $V_{\rm ds}$  = 0.1 V.

Fig.2. Si NW FFFET memory device. (a) A schematic view of a back gate FEFET based nonvolatile memory device and operation mechanism. (b) A hysteretic behavior for a back gate Si NW FEFET coated with PVDF on the NW surface.

Fig.3. Memory characteristics of a Si NW FEFET (coated with PVDF) based memory. (a) Retention times and (b) Endurance tests evolution of the drain currents of the Si NW FEFET device.